Design Intent

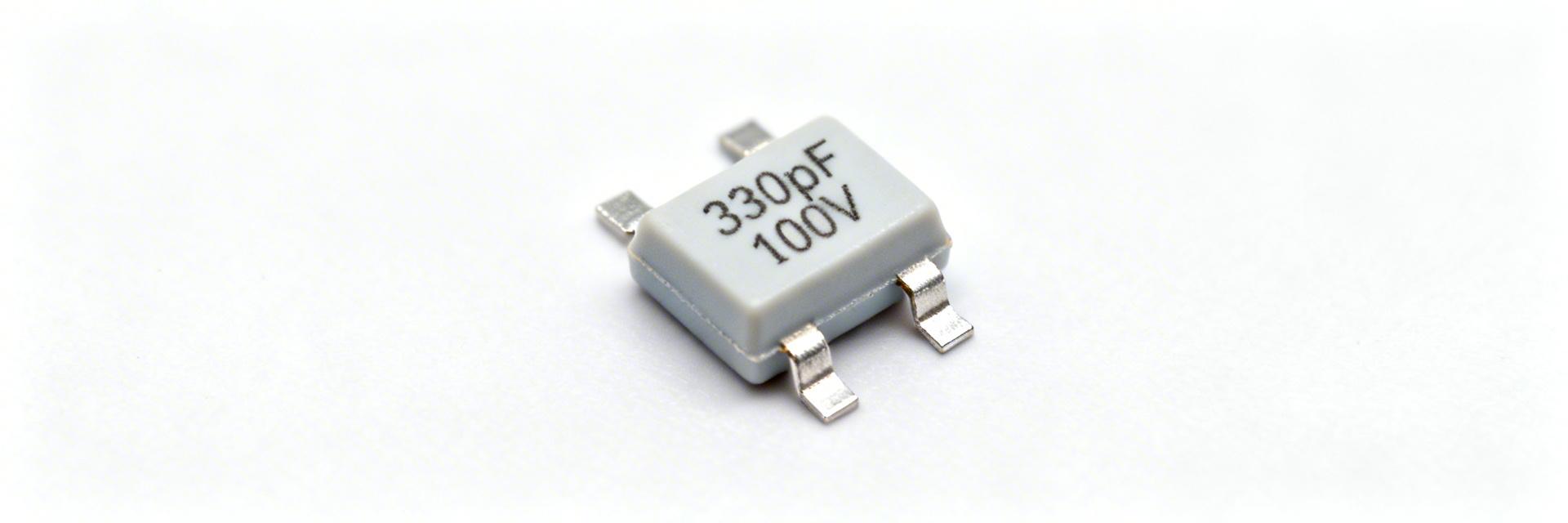

Engineers specifying stable small-value capacitors often select NP0 (C0G) MLCCs for minimal capacitance drift and low loss. The MLCC 06031A331J4T2A combines a 330pF nominal value with a 100V rating and NP0 dielectric, making it suited to timing, RF front-end, and precision analog reference circuits where stability is critical.

Technical Scope

This article summarizes the key electrical and mechanical specs, practical DC-bias and frequency behavior, test recommendations, layout tips, and a procurement checklist, drawing on standard lab test practices for production-ready designs.

At-a-glance spec summary for MLCC 06031A331J4T2A

Electrical Datasheet Snapshot

Core electrical specs define suitability for precision designs. For MLCC 06031A331J4T2A, the footprint is optimized for minimal temperature and bias drift.

| Parameter | Typical Value |

|---|---|

| Nominal Capacitance | 330 pF |

| Tolerance | ±5% (J) |

| Rated Voltage | 100 V DC |

| Temp. Coefficient | NP0 / C0G (~0 ±30 ppm/°C) |

| Case Code | 0603 (06031 Footprint) |

Dielectric Stability Comparison

Note: NP0 maintains near-zero drift across temperature ranges (-55°C to +125°C).

Datasheet Deep-dive: What the Numbers Mean in Practice

Capacitance, Tolerance, and Stability

NP0 dielectric delivers exceptional stability. conceptually specified around 0 ±30 ppm/°C, translating to negligible capacitance drift across typical operating ranges. This stability makes 330pF NP0 parts ideal for oscillator load caps, ADC reference bypass, and RF matching where dielectric absorption would degrade performance.

Voltage Rating vs. DC Bias Behavior

While DC bias can reduce effective capacitance in ceramic MLCCs, NP0 is far less sensitive than high-K dielectrics. For a 100V-rated 330pF NP0 part, expect only a few percent change under moderate bias. Still, precision designs should include margin and quantify derating if necessary.

Electrical Performance & Test Considerations

Frequency Response, ESR/ESL, and Self-Resonant Frequency (SRF) +

Reliability and Environmental Testing Requirements +

PCB Layout and Assembly Tips +

Alternatives and Trade-offs

Dielectric Choice

NP0/C0G offers the lowest drift. While trading to X7R/X5R might offer higher density, it requires mitigating significant temperature and bias drift through calibration or larger safety margins.

Case Size Optimization

Upsizing from 0603 to 0805 increases voltage margin and eases assembly. However, 0603 remains the standard for balancing board area with performance in compact precision designs.

Procurement & Test Checklist

- ✓ Request capacitance vs. voltage and temperature coefficient tables from the supplier.

- ✓ Verify MSL rating and obtain the recommended reflow profile.

- ✓ Implement incoming inspection: sample batch DC-bias and capacitance distribution checks.

- ✓ Ensure lot traceability and anti-counterfeit clauses are present in supplier agreements.